| - Home page |

| - No.305 目次 |

| + 宇宙科学最前線 |

| - お知らせ |

| - ISAS事情 |

| - 科学衛星秘話 |

| - ロケットの電気屋さん |

| - 東奔西走 |

| - いも焼酎 |

| - 宇宙・夢・人 |

| - 編集後記 |

| - BackNumber |

|

※1 CMOS:Complementary metal-oxide semiconductor MOSは,ゲート電極によって半導体表面の伝導度を制御することができるようになっている。特に,ゲートに印加する電圧による応答が相補的な2種類のトランジスタを具備しているものをCMOSという。 |

|---|

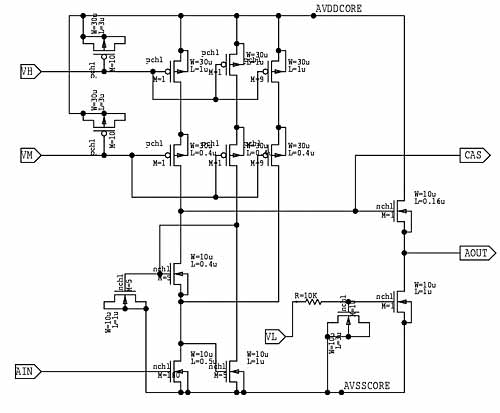

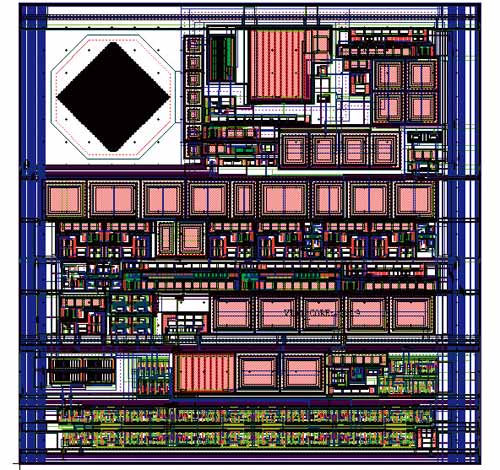

宇宙科学研究本部では,X線ないしγ線領域におけるエネルギー弁別とイメージング観測を目的として,ピクセル化されたシリコンないしカドミウムテルライドをセンサーとするシステムの開発を進めています。このような開発の一環として,Open-IPを用いて4096チャンネル構成のピクセル型ASIC※2の試作開発が行われています。試作チップは,200μm×200μmのピクセル領域に,荷電増幅器,整形増幅器,ピークホールド回路,アナログマルチプレクサ,ならびにテストパルス回路およびディジタル制御回路などを含んでいます。本試作チップでは,ピクセル当たり150μWの低電力特性と,100電子相当以下の雑音レベルを達成することを目指しています。これは,バイアス回路の安定化,電源感度の最小化,半導体プロセスの選択など多面的な設計によって実現されています。図1に1ピクセル分の回路のレイアウト図を示しました。図中左上部に設けられたボンディングパッド部のところで,放射線センサーとバンプ(金属の微小な突起)を用いて接続されるようになっています。最初の試作チップは,TSMC社の0.25μm CMOSプロセスによって設計・製造後,基本的な動作が確認され,二次試作に向けての準備が進行中です。

|

※2 ASIC:Application specific integrated circuit 「特定用途向け集積回路」と訳されるのが一般的。生産数量は少なくても,応用技術に最適な製品を供給すべく開発されているのがASIC。 |

|---|

|

|---|

| 図1 200μm四方のピクセル回路のレイアウト 下辺部付近の密集したディジタルの制御回路を除いては,ほとんどがアナログ信号処理回路によって占められている。 |

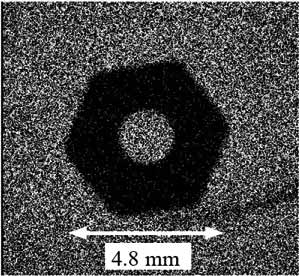

大阪大学でも,X線天文用のCCD読み出しシステムを開発しています。CCDは,信号対雑音比において優れた性能を発揮するものの,読み出し時間において相対的に劣るという問題があります。そこで,読み出し時間を短縮するために,CCDチップに複数の読み出しポートを設け,これを専用のASICで読み出すことが試みられています。このようなCCD読み出しチップは,ポートごとに,積分回路とホールド回路からなる雑音フィルター回路と,12ビットのグレイコードカウンタを用いたウィルキンソン型のA/D変換回路を必要とします。また,二重相関サンプリングを用いることにより,10電子以下の雑音レベルを達成することを目指しています。図2には,この集積回路を用いて撮像されたX線画像を示しました。大阪大学では,Open-IPを拡張して,ΔΣコンバータを用いた信号処理系の試作にも着手しています。

|

|---|

| 図2 X線検出器用のCCDからの信号を試作チップで読み出した画像 M2.6のナットによってX線が遮蔽されている。 |